比亚迪

半导体

# BF20A6 Datasheet

## 1/10 inch VGA SOC CMOS Image Sensor With DVP and SPI

**BF20A6**

**Datasheet**

Apply to: BF20A6CS、BF20A6CS-T

# Content

|                                                           |    |

|-----------------------------------------------------------|----|

| 1. General Description.....                               | 3  |

| 2. Features.....                                          | 3  |

| 3. Applications.....                                      | 3  |

| 4. Technical Specifications.....                          | 4  |

| 5. Functional Overview.                                   | 4  |

| 5.1 Pixel Array.....                                      | 5  |

| 5.2 Lens Chief Ray Angle (CRA).....                       | 6  |

| 5.3 Column CDS.....                                       | 6  |

| 5.4 Sensor control.....                                   | 7  |

| 5.5 A/D converter.....                                    | 7  |

| 5.6 Automatic Black Control.....                          | 7  |

| 6. Specifications.....                                    | 7  |

| 6.1 Electrical Characteristics.....                       | 7  |

| 6.1.1 Absolute Maximum Ratings.....                       | 7  |

| 6.1.2 DC Parameters.....                                  | 7  |

| 6.1.3 Clock Requirement.....                              | 8  |

| 6.2 Electro-Optical Characteristics.....                  | 8  |

| 6.3 Timing.....                                           | 9  |

| 6.3.1 The inner VGA Frame Timing.....                     | 9  |

| 6.4 Color Filter Spectral Characteristics.....            | 9  |

| 7. Two-wire serial interface& Register.....               | 10 |

| 7.1 Theory of Operation.....                              | 10 |

| 7.2 Two-wire Serial Interface Functional Description..... | 11 |

| 7.3 The Two-wire Serial Interface Timing.....             | 12 |

| 7.4 Register Summary (full list).....                     | 12 |

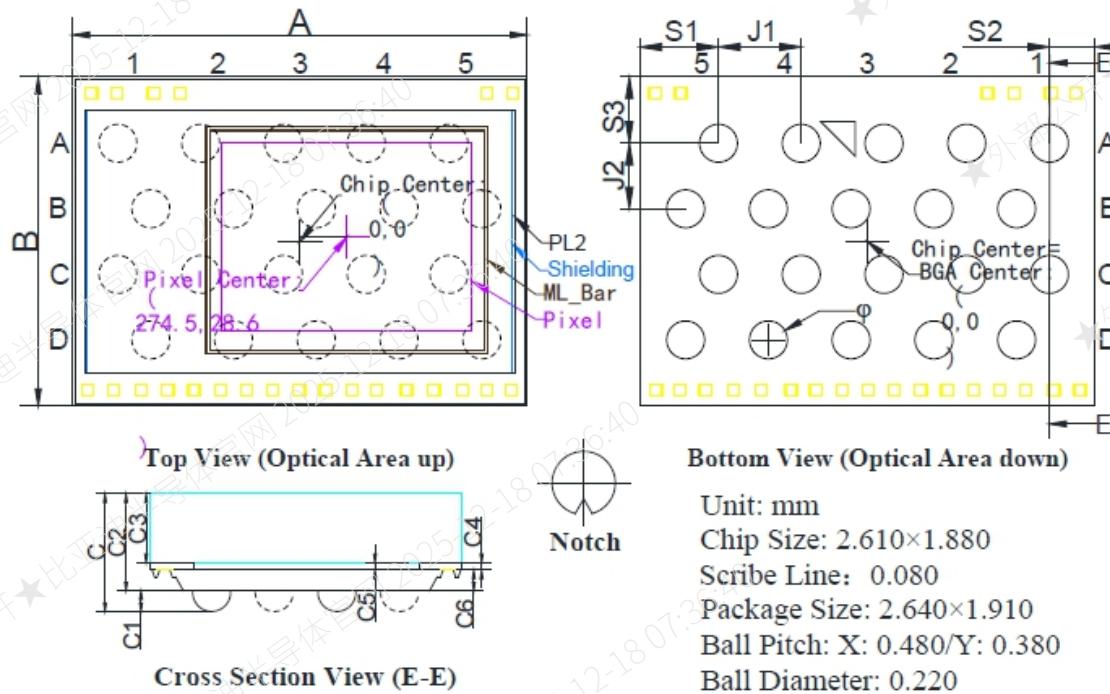

| 8. Package Specifications.....                            | 24 |

| 8.1 CSP Package.....                                      | 25 |

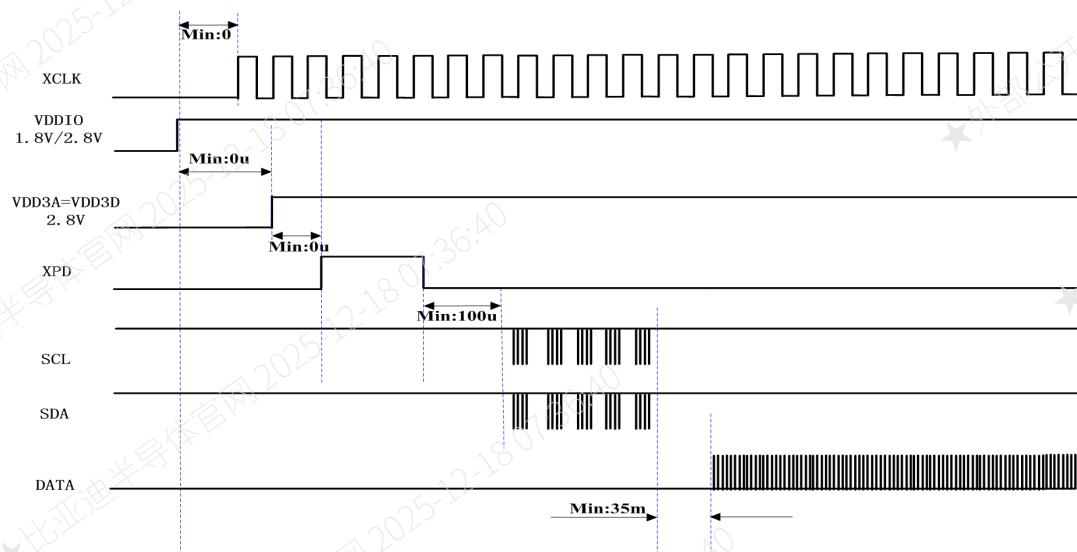

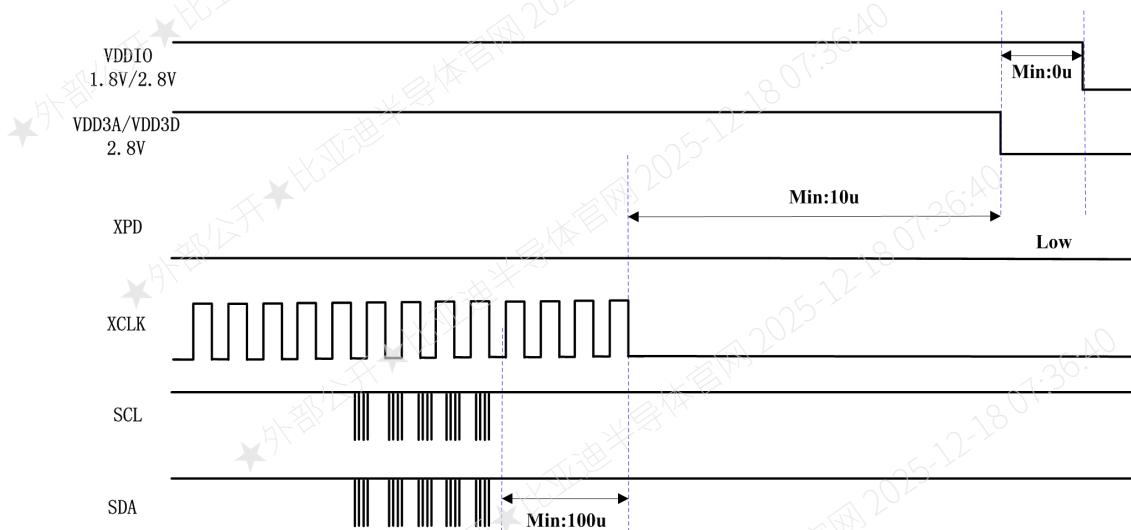

| 9. Application Timing Diagram.....                        | 27 |

## 1. General Description

The BF20A6 is a 1/10-inch VGA CMOS Image Sensor which includes CMOS image sensor (CIS) and ISP. It is fabricated with the world's most advanced CIS process to realize ultra-low dark noise, high sensitivity, high dynamic range and very low power imaging system. The sensor consists of a 640×480 pixel array which has an optical format of 1/10 inch for VGA. It has integrated noise canceling CDS circuits, analog global gain and separated R/G/B gain controller, automatic black level compensation and on-chip 10-bit ADC. The on-chip ISP provides a very smooth AE and accurate AWB control. It provides various data formats, such as Bayer RGB, YCbCr 4:2:2. It has a commonly used two-wire serial interface for host to control the operation of the whole sensor.

The product is capable of operating at up to 30 frames per second at 12MHz master clock in VGA mode, with complete user control over image quality and data format. All required image processing functions are also programmable through the two-wire serial bus.

## 2. Features

- Standard optical format of 1/10 inch for VGA

- 30 frames/sec VGA mode.

- Ultra-low dark noise at high temperature.

- Ultra-Low power consumption

- $\leq 70 \text{ mW}@30\text{fps}$  VGA

- $\leq 180 \text{ uA}@$  power down

- Output formats: YUV422/Raw/ Only Y

- Power supply: 1.8/ 2.8V for I/O, 2.8V for VDD3A/VDD3D

- Horizontal /Vertical mirror.

- Auto black level control.

- Image processing function: Gamma Correction, Bad Pixel Correction, Color Interpolation, Low Pass Filter, Color Space Conversion, Color Correction, Edge Enhancement, Auto exposure, Auto White Balance, Color Saturation, Contrast, Skin Detection, and Data Format Conversion. Exposure control, Gain control, Test pattern, Image size control, Lens shading, Gamma and so on.

- Package: CSP.

## 3. Applications

- Cellular Phone Cameras

- Notebook PC cameras

- PDAs

- MP4

- Digital still cameras and camcorders

- Video telephony and conferencing equipment.

## 4. Technical Specifications

|                                 |                    |

|---------------------------------|--------------------|

| ● Active pixel array:           | 640*480            |

| ● Pixel size:                   | 2.25um×2.25um      |

| ● Sensitivity:                  | 1.35V/Lux·sec      |

| ● Dark current:                 | ≤2 mV/s at 25°C    |

| ● Power supply:                 | 2.8V/1.8V          |

| ● Power consumption:            | ≤70 mW@30fps (VGA) |

| ● Standby current:              | ≤180 uA            |

| ● S/N Ratio:                    | 37 dB              |

| ● Dynamic range:                | 60 dB              |

| ● Operating temperature:        | -10~65°C           |

| ● Stable Image temperature:     | 0~60°C             |

| ● Optimal lens chief ray angle: | 28° non-linear     |

| ● Package:                      | CSP                |

## 5. Functional Overview

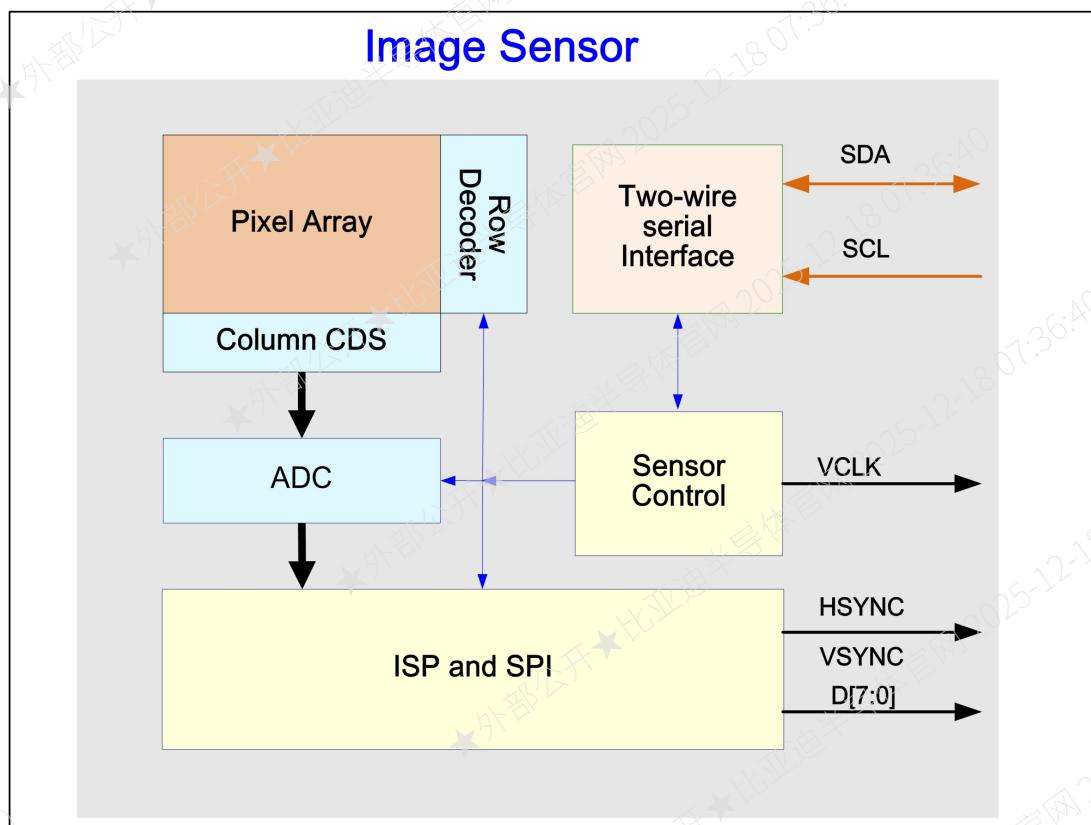

Figure 1. Block Diagram

BF20A6 has an active image array of 640x480 pixels. The active pixels are read out progressively through column/row driver circuits. In order to reduce fixed pattern noise, CDS circuits are adopted. The

analog signal is transferred to digital signal by A/D converter. It provide global gain to get accurate exposure under different light condition. The digital signals are controlled by Sensor control Block, including Exposure control, Gain control, Test pattern, Image size control and so on.

BF20A6 has on-chip PLL, it can be used by via two-wire serial interface bus setting.

## 5.1 Pixel Array

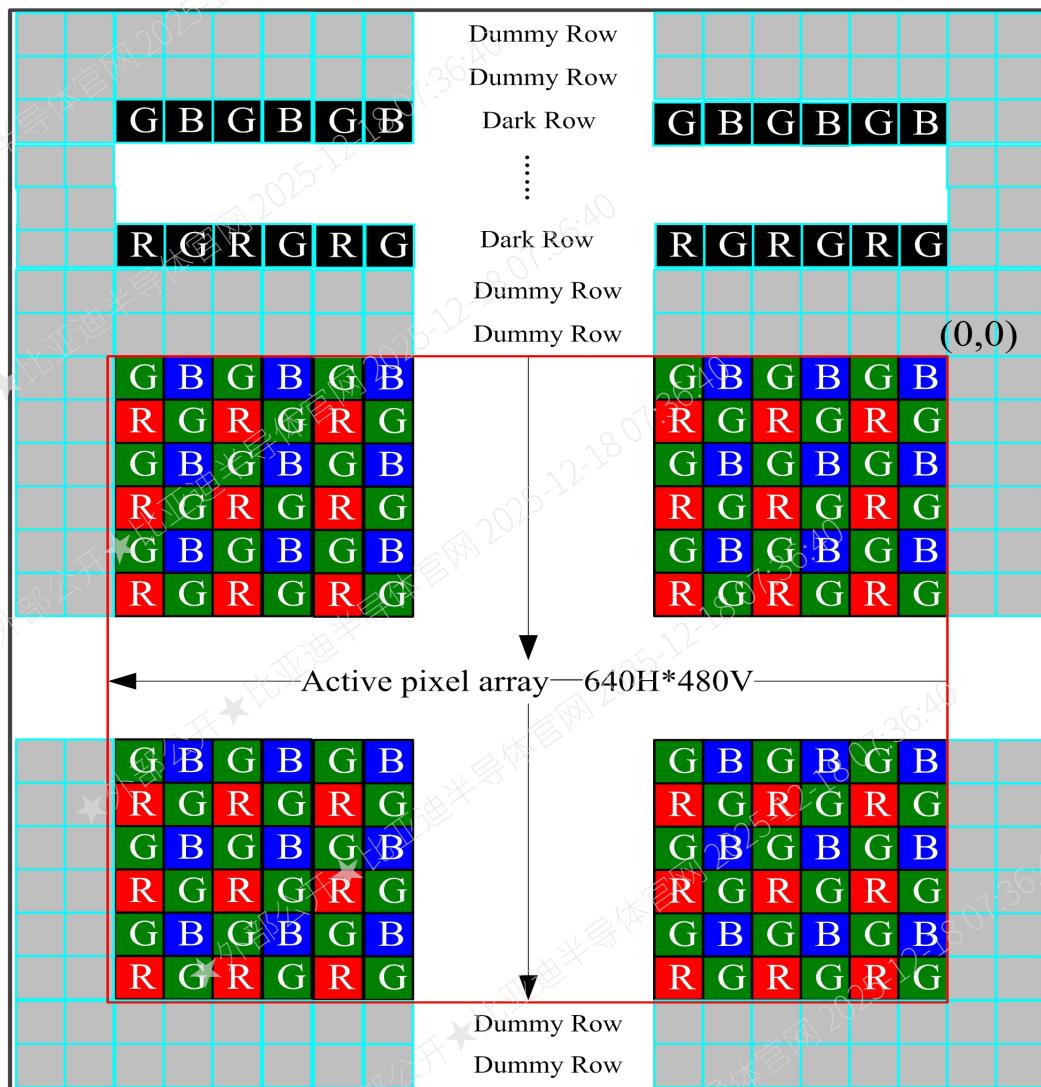

Figure 2. Sensor Array Region

The pixel array includes 640x480 effective pixels for imaging, whose address range is from (0, 0) to (639, 479). There are extra dark rows at the top side for black level control.

Pixel array is covered by Bayer color filters as can be seen in the figure2. The primary color BG/GR array is arranged in line-alternating fashion. Since each pixel can have only one type of color filter on it, only one color component can be obtained by a pixel. BF20A6 can provide the Raw Bayer data , YUV data and Only Y through SPI and DVP interface. If flip or not in column.

## 5.2 Lens Chief Ray Angle (CRA)

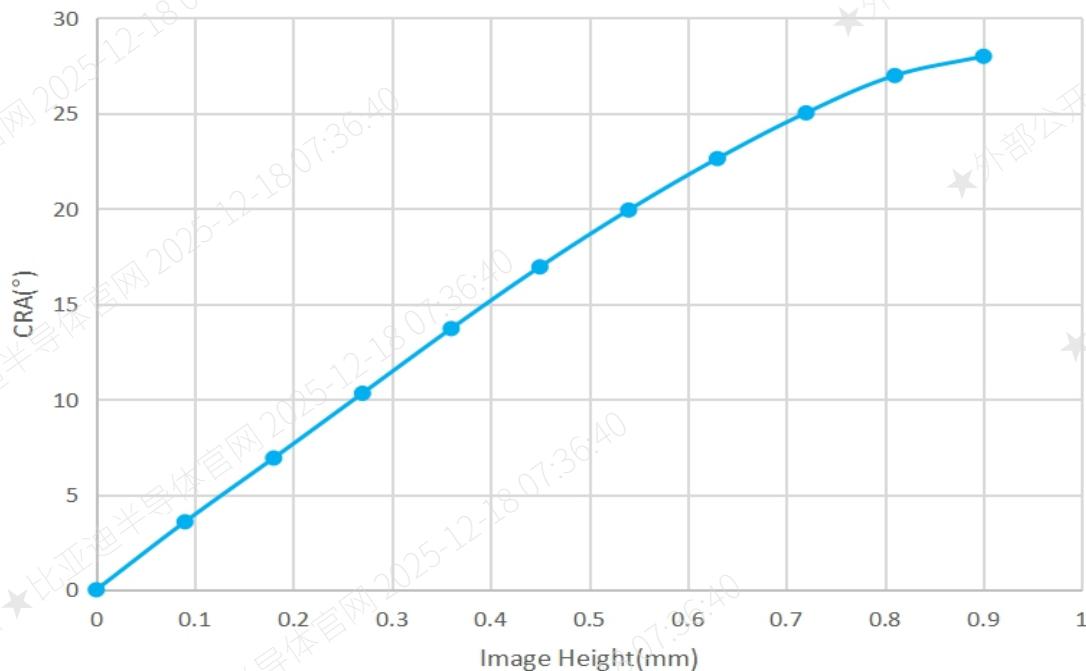

Figure 3. CRA information

Table 1. CRA versus image height plot

| Field | Image Height(mm) | CRA(degree) |

|-------|------------------|-------------|

| 0     | 0                | 0           |

| 10%   | 0.09             | 3.57        |

| 20%   | 0.18             | 6.91        |

| 30%   | 0.27             | 10.31       |

| 40%   | 0.36             | 13.71       |

| 50%   | 0.45             | 16.95       |

| 60%   | 0.54             | 19.93       |

| 70%   | 0.63             | 22.63       |

| 80%   | 0.72             | 25.03       |

| 90%   | 0.81             | 26.99       |

| 100%  | 0.9              | 28.00       |

## 5.3 Column CDS

BF20A6 has column/row driver circuits to read out the pixel data progressively. The CDS (Correlated Double Sampling) circuit reduces temporal noise and pixel level FPN (Fixed Pattern Noise). The unique patented column buffer and ADC circuit remove column level FPN caused by various sources of

manufacturing process variations.

## 5.4 Sensor control

- Array control and frame generation

- Internal timing signal generation and distribution

- Exposure control, Gain control, Test pattern,

- Image size control

- Frame rate timing

## 5.5 A/D converter

The analog signals are converted to digital forms and data are streamed out column by column. BF20A6 provides the 10-bit Raw Bayer data through an internal 10-bit data bus.

## 5.6 Automatic Black Control

The automatic black level control calculates the data of the dark row and controls the lowest black level for output image data.

# 6. Specifications

## 6.1 Electrical Characteristics

### 6.1.1 Absolute Maximum Ratings

- |                                 |             |

|---------------------------------|-------------|

| ● Supply voltage (VDDIO):       | 1.7 ~ 3.1 V |

| ● Supply voltage (VDD3A/VDD3D): | 2.7~3.1V    |

| ● Operating temperature:        | -10°C~65°C  |

| ● Storage temperature:          | -40°C~85°C  |

| ● ESD Rating, Human Body mode:  | 2000 V      |

Caution: Stresses exceeding the absolute maximum ratings may induce failure.

### 6.1.2 DC Parameters

Table 2. DC Operation Conditions

| Symbol | Parameter                | Unit | Min.      | Typ. | Max.      | Notes |

|--------|--------------------------|------|-----------|------|-----------|-------|

| VDDIO  | I/O power supply         | V    | 1.7       | 1.8  | 3.1       | 1     |

| VDD3A  | Analog power supply      | V    | 2.7       | 2.8  | 3.1       | --    |

| VDD3D  | Analog power supply      | V    | 2.7       | 2.8  | 3.1       | --    |

| Vih    | Input voltage logic "1"  | V    | 0.7*VDDIO | --   | --        | --    |

| Vil    | Input voltage logic "0"  | V    | --        | --   | 0.2*VDDIO | --    |

| Voh    | Output voltage logic "1" | V    | 0.9*VDDIO | --   | --        | --    |

| Vol    | Output voltage logic "0" | V    | --        | --   | 0.1*VDDIO | --    |

| Symbol  | Parameter                                      | Unit | Min.     | Typ. | Max. | Notes |

|---------|------------------------------------------------|------|----------|------|------|-------|

| I_vddio | VDDIO supply current,<br>normal operation mode | mA   | --       | 15   | 22   |       |

| I_vdd3d | VDD3D supply current,                          | mA   | --<br>-- | 1    | 2    | 2     |

| I_vdd3a | VDD3A supply current,                          | mA   | --       | 9    | 15   | 2     |

Note:

1. VDDIO=1.8V/ 2.8V (30 fps)

2. The Current of power is decided by the work mode, ex. Frequency of clock and output format. The Max. Current will not appear at the same time.

### 6.1.3 Clock Requirement

Table 3. AC Operation Conditions

| Symbol | Parameter                                 | Unit | Min. | Typ. | Max. | Notes |

|--------|-------------------------------------------|------|------|------|------|-------|

| XCLK   | External input clock                      | MHz  | --   | 24   | --   | 1     |

| PCLK   | Pixel clock of the system                 | MHz  | --   | 12   | --   | 2     |

| VCLK   | DVP Output clock                          | MHz  | --   | 24   | --   | 3     |

| SCLK   | two-wire serial interface clock frequency | KHz  | --   | 400  | --   | 4     |

Note:

1. XCLK is the input clock of system as the input of PLL.

2. PCLK is the pixel clock of system, and it is generated by PLL.

3. VCLK is the DVP output clock when the VCLK Pin is defined.

(Raw: VCLK=PCLK; YUV: VCLK=2\*PCLK)

4. SCLK is driven by host processor. For the detail serial bus timing, refer to two-wire serial Interface section

## 6.2 Electro-Optical Characteristics

Clock frequency: 12MHz.

Operating voltage: VDDIO=2.8V, VDD3D=2.8V, VDD3A=2.8V.

Operating temperature: 25°C

Table 4. Electro-Optical Characteristics

| Parameter     | Unit      | Min. | Typ. | Max. | Notes |

|---------------|-----------|------|------|------|-------|

| Sensitivity   | V/Lux·sec | --   | 1.35 |      | 1     |

| Dark current  | mV/sec    | --   | 1    | --   | 2     |

| S/N ratio     | dB        | --   | 37   | --   | --    |

| Dynamic Range | dB        | --   | 60   | --   | --    |

| Frame Rate    | fps       | --   | 30   | 30   | 3     |

Notes:

1. With color filter, measured at 50 lux green light condition at room temperature.

2. Measured at dark condition for exposure time of 1s (25 Celsius).

3. With 640×480 at PCLK 12MHz.

## 6.3 Timing

### 6.3.1 The inner VGA Frame Timing

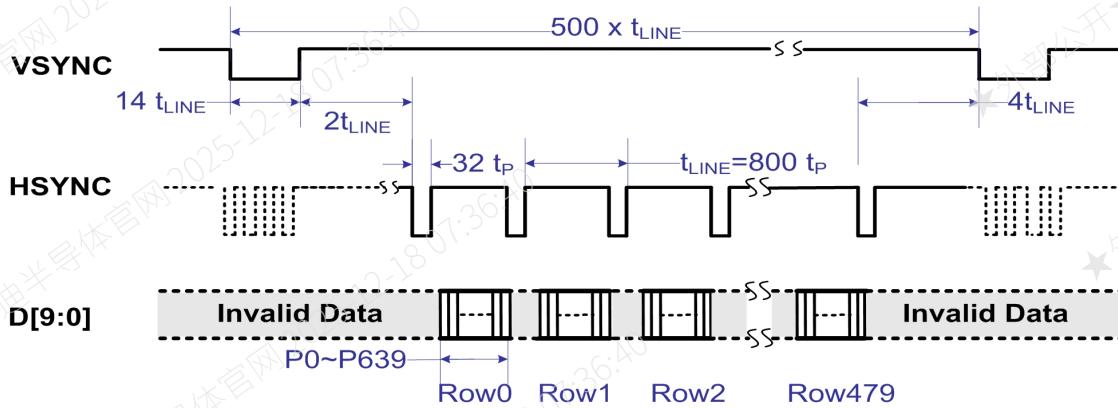

Figure 4. Inner VGA Frame Timing

Table 5. AC Characteristics

| Symbol     | Descriptions          | Min. | Typ.             | Max. | Unit |

|------------|-----------------------|------|------------------|------|------|

| $t_P$      | Pixel clock period    | --   | 83.3             | --   | ns   |

| $f_{PCLK}$ | Pixel Clock Frequency | --   | 12               | --   | MHz  |

| $t_{LINE}$ | Line length           | --   | $800 \times t_P$ | --   | ns   |

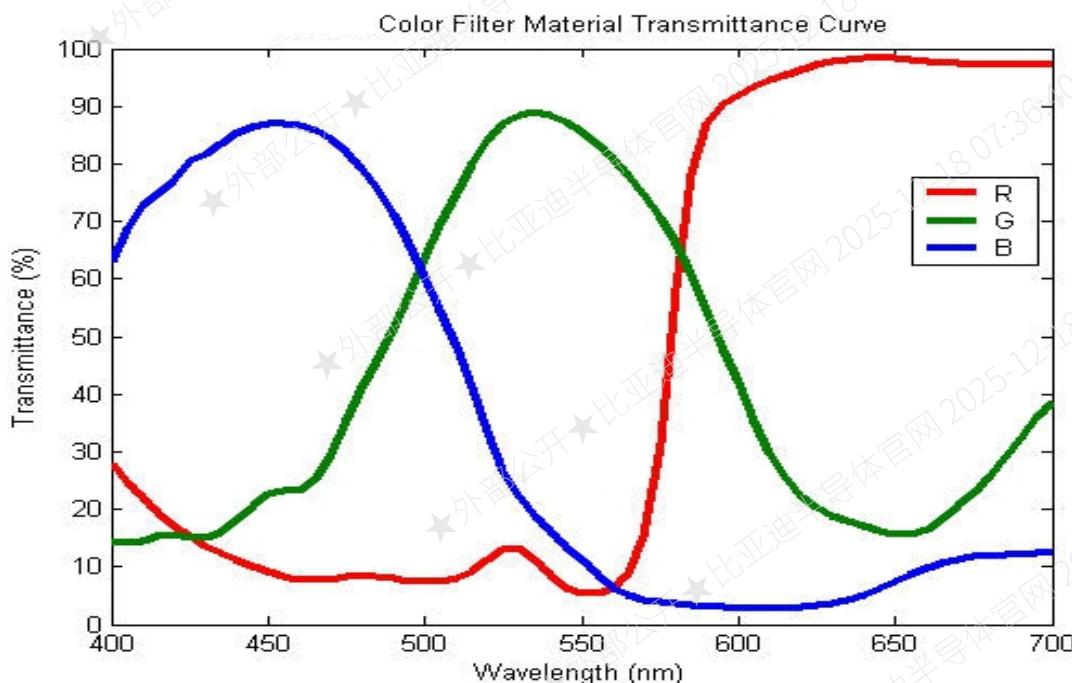

## 6.4 Color Filter Spectral Characteristics

The optical spectrum of color filters is shown below.

Figure 5. Spectral Characteristics

## 7. Two-wire serial interface& Register

### 7.1 Theory of Operation

The registers of BF20A6 are written and read through the two-wire serial interface. BF20A6 has two-wire serial interface slave. BF20A6 is controlled by the two-wire serial interface clock (SCLK), which is driven by the two-wire serial interface master. Data is transferred into and out of BF20A6 through the two-wire serial interface data (SDA) line. The SCL and SDA lines are pulled up to VDDIO by a  $2\text{k}\Omega$  off-chip resistor. Either the slave or the master device can pull the lines down. The two-wire serial interface protocol determines which device is allowed to pull the two lines down at any given time.

**Note:** Two-wire serial interface device address of BF20A6 is 7'b1101110 (0X6e), it doesn't include W/R bit.

#### Start bit

The start bit is defined as a HIGH to LOW transition of the data line while the clock line is HIGH.

#### Stop bit

The stop bit is defined as a LOW to HIGH transition of the data line while the clock line is HIGH.

#### Slave Address

The 8-bit address of a two-wire serial interface device consists of 7 bits of address and 1 bit of direction. A0 in the LSB of the address indicates write mode, and A1 indicates read-mode.

#### Data bit transfer

One data bit is transferred during each clock pulse. The two-wire serial interface clock pulse is provided by the master. The data must be stable during the HIGH period of the two-wire serial interface clock: it can only change when the two-wire serial interface clock is LOW. Data is transferred 8 bits at a time, followed by an acknowledge bit.

#### Acknowledge bit

The receiver generates the acknowledge clock pulse. The transmitter (which is the master when writing, or the slave when reading) releases the data line, and receiver indicates an acknowledge bit by pulling the data line low during the acknowledge clock pulse.

#### No-acknowledge bit

The no-acknowledge bit is generated when the data line is not pulled down by the receiver during the acknowledge clock pulse. A no-acknowledge bit is used to terminate a read sequence.

#### Sequence

A typical read or write sequence begins by the master sending a start bit. After start bit, the master sends the slave device's 8-bit address. The last bit of the address determines if the request will be a read or a write, where a 0 indicates a write and a 1 indicates a read. The slave device acknowledges its address by sending an acknowledge bit back to the master.

If the request was a write, the master then transfers the 8-bit register address to which a write should take place. The slave sends an acknowledge bit to indicate that the register address has been received. The master then transfers the data 8 bits at a time, with the slave sending an acknowledge bit after each 8 bits. The BF20A6 uses 8 bit data for its internal registers, thus requiring one 8-bit transfer to write to one register. After 8 bits are transferred, the register address is automatically incremented, so that the next 8 bits are written to the next register address. The master stops writing by sending a start or stop bit.

A typical read sequence is executed as follows. First the master sends the write-mode slave address and 8-bit register address just as in the write request. The master then sends a start bit and the read-mode slave address. The master then clocks out the register data 8 bits at a time. The master sends an acknowledge bit after each 8-bit transfer. The register address is auto-incremented after each 8 bit is transferred. The data transfer is stopped when the master sends a no-acknowledge bit.

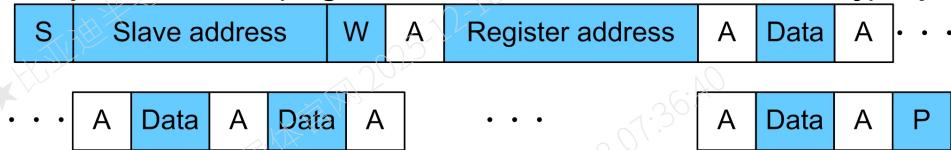

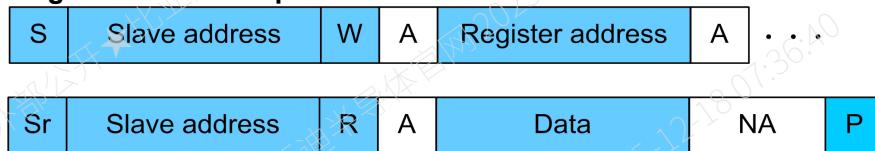

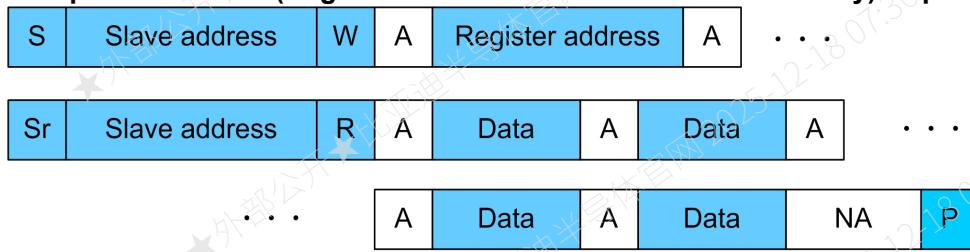

## 7.2 Two-wire Serial Interface Functional Description

### Single Write Mode Operation

### Multiple Write Mode (Register address is increased automatically)<sup>1</sup> operation

### Single Read Mode Operation

### Multiple Read Mode (Register address is increased automatically)<sup>1</sup> Operation

From master to slave

S: Start condition.

From slave to master

Sr: Repeated Start (Start without preceding stop.)

#### Slave Address:

write address = 0xdc = 11011100b

read address = 0xdd = 11011101b

R/W: Read/Write selection. High = read, LOW = write.

A: Acknowledge bit. NA: No Acknowledge.

Data: 8-bit data P: Stop condition

**Note1:** Continuous writing or reading without any interrupt increases the register address automatically. If the address is increased above valid register address range, further writing does not affect the chip operation in write mode. Data from invalid registers are undefined in read mode.

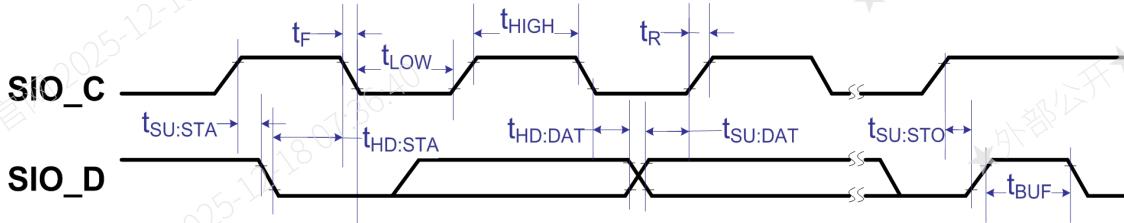

### 7.3 The Two-wire Serial Interface Timing

Figure 6. Two-Wire Serial Interface Timing

Table 6. AC Characteristics

| Symbol       | Descriptions                              | Min. | Typ. | Max. | Unit |

|--------------|-------------------------------------------|------|------|------|------|

| $t_R, t_F$   | two-wire serial interface rise/fall times | --   | --   | 300  | ns   |

| $t_{LOW}$    | Clock Low Period                          | 1.3  | --   | --   | us   |

| $t_{HIGH}$   | Clock High Period                         | 600  | --   | --   | ns   |

| $t_{HD:STA}$ | Start condition Hold Time                 | 600  | --   | --   | ns   |

| $t_{SU:STA}$ | Start condition Setup Time                | 600  | --   | --   | ns   |

| $t_{HD:DAT}$ | Data-in Hold Time                         | 0    | --   | --   | ns   |

| $t_{SU:DAT}$ | Data-in Setup Time                        | 100  | --   | --   | ns   |

| $t_{SU:STO}$ | Stop condition Setup Time                 | 600  | --   | --   | ns   |

### 7.4 Register Summary (full list)

Table 7. BF20A6 all registers

| Address | Name                    | Width | Default value | Description                                                                                                                                                                                                                                                     |

|---------|-------------------------|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 00h     | <b>MODE_CNTL</b>        | 8     | 23h           | Bit[7]: BYPASS_BC<br>1'b1:Bypass digital black cntl.<br>1'b0:Don't bypass digital black cntl.<br>Bit[6]: Reserved.<br>Bit[5:4]: Dark row select.<br>Bit[3]: Black level adjust mode.<br>Bit[2]: Channel select.<br>Bit[1]: Adjust mode.<br>Bit[0]: Adjust mode. |

| 01h     | <b>BLUE_GAIN</b>        | 6     | 1ah           | Blue gain 7bit for outdoor scene,<br>6 bits for indoor scene.                                                                                                                                                                                                   |

| 02h     | <b>RED_GAIN</b>         | 6     | 1ah           | Red gain 7bit for outdoor scene,<br>6 bits for indoor scene.                                                                                                                                                                                                    |

| 03h     | <b>VBLANK_PIX[12:8]</b> | 5     | 00h           | Bit[7:5]: Reserved.<br>Bit[4:0] :VBLANK_PIX[12:8].                                                                                                                                                                                                              |

| 04h     | <b>HSYST_LOCK</b>       | 8     | 02h           | Control the rising edged of HSYNC.                                                                                                                                                                                                                              |

| 05h     | <b>HSYEN_LOCK</b>       | 8     | 20h           | Control the falling edged of HSYNC.                                                                                                                                                                                                                             |

| 06h     | <b>DARKE_AVER</b>       | 8     | RO            | Current black level                                                                                                                                                                                                                                             |

| Address | Name                     | Width | Default value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  |

|---------|--------------------------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 07h     | <b>DARKO_AVER</b>        | 8     | RO            | Current black level                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0bh     | <b>COM3</b>              | 8     | 00h           | Bit[7]: Adjust to CCIR packet code<br>Bit[6]: Row counter after window<br>Bit[5]: UV output value select.<br>Bit[4]: DAT counter delay select.<br>Bit[3:0]: Frame counter for skip.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 0ch     | <b>AVER_LOCK</b>         | 8     | 32h           | Bit[7:4]: Lock value1<br>Bit[3:0]: Lock value2                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 0dh     | <b>H_HSYNC_EDGE_LOCK</b> | 8     | 00h           | Bit[7:4]: HSYNC rising edge[11:8]<br>Bit[3:0]: HSYNC falling edge[11:8]                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                      |

| 0eh     | <b>SH_Timing</b>         | 8     | 1fh           | SH_Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 0fh     | <b>SH_Timing</b>         | 8     | 24h           | SH_Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 10h     | <b>SH_Timing</b>         | 8     | 39h           | SH_Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 11h     | <b>SH_Timing</b>         | 8     | 3ch           | SH_Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| 12h     | <b>COM0</b>              | 8     | 20h           | Bit[7]:DAT_FOUR_SWAP.<br>1'b1:enable 1'b0:disable.<br>Bit[6]:High byte and Low byte crossing-over of CODE:<br>1'b0: Low/High 1'b1: High/Low<br>Bit[5]: Zhan xun or mtk ccir packet swap control :<br>1'b1:swap , 1'b0: no swap .<br>Bit[4]: Zhan xun or mtk ccir packet select control:<br>1'b1:select zhan xun ccir ,1'b0:select mtk ccir<br>Bit[3]: 1'b0: Output 8'h00 during hblank<br>1'b1: Output normally during hblank<br>Bit[2]: Process RAW and bayer RAW Selection.<br>1'b0:bayer RAW 1'b1:process RAW<br>Bit[1]: DOMAIN_SEL, for Only Y mode.<br>Bit[0]: Raw RGB Selection.<br>YCBYCR:x0. RAW:x1. |

| 13h     | <b>COM8</b>              | 8     | 05h           | Bit[7] 1'b1:AE_TAR<br>1'b0:AE_TAR MODIFY<br>Bit[6]: Select INT_TIM.<br>Bit[5]: AE adjusts rate.<br>Bit[4]: The MSB of the minimum integral time for every step to avoid flicker for 50HZ/60HZ light.<br>Bit[3]: GLB_GAIN0 written when AGC disable<br>Bit[2]: AGC Enable.<br>Bit[1]: Digital gain switch.<br>1'b0:OFF 1'b1:ON.<br>Bit[0]: AEC Enable.<br>1'b0:OFF , 1'b1: ON.                                                                                                                                                                                                                                |

| 14h     | <b>P_PIXEL_OE</b>        | 8     | RO            | Reserved.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    |

| Address | Name              | Width | Default value | Description                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

|---------|-------------------|-------|---------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 15h     | <b>COM1</b>       | 8     | 00h           | Bit[7]: VCLK reverse ,before gated latch<br>Bit[6]: Hsync select before window<br>1'b0: no hsync when vsync_dat=0<br>1'b1: always has hsync<br>Bit[5]: VSYNC output selection befor packet code,<br>1'b0: VSYNC_IMAGE.<br>1'b1: VSYNC_DAT<br>Bit[4]: VCLK reverse, after gated latch<br>Bit[3]: HSYNC output select befor code,<br>1'b0: HSYNC:<br>1'b1: HREF.<br>Bit[2]: 1'b0: no HREF when VSYNC_DAT=0.<br>1'b1: always has HREF or not.<br>Bit[1]: Negative image enable<br>1'b0: Normal image.<br>1'b1: Negative image<br>Bit[0]: Negative enable<br>1'b0: Normal<br>1'b1: Negative pixel |

| 16h     | <b>COM2</b>       | 8     | 70h           | Bit[7]: Hsync mode after window:<br>Bit[6]: Posedge and negedge of VSYNC in the MTK mode :<br>1'b1:enable. 1'b0:disable<br>Bit[5]: Posedge of HSYNC in the MTK mode :<br>1'b1:enable 1'b0:disable<br>Bit[4]: Posedge of HREF in the MTK mode :<br>1'b1:enable. 1'b0:disable<br>Bit[3:2]: YUV Select.<br>2'b00:YUYV. 2'b01:UYVY.<br>2'b10:YVYU. 2'b11:VYUY.<br>Bit[1]: CKGATE ahead Select.<br>Bit[0]: GATED clock Select.<br>1'b0: Disable. 1'b1: Enable.                                                                                                                                     |

| 17h     | <b>HSTART</b>     | 8     | 00h           | Output Format-Horizontal Frame start high 8-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 18h     | <b>HSTOP</b>      | 8     | a0h           | Output Format-Horizontal Frame end high 8-bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 19h     | <b>VSTART</b>     | 8     | 00h           | Output Format-Vertical Frame start high 8-Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| 1ah     | <b>VSTOP</b>      | 8     | 78h           | Output Format-Vertical Frame end high 8-Bit                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                   |

| 1bh     | <b>VHREF</b>      | 8     | 00h           | Bit[7:6]: Output Format-Vertical Frame(row)end low 2-Bit<br>Bit[5:4]: Output Format-Vertical Frame(row)start low 2-Bit<br>Bit[3:2]: Output Format-Horizontal Frame end low 2-bit<br>Bit[1:0]: Output Format-Horizontal Frame start low 2-bit                                                                                                                                                                                                                                                                                                                                                  |

| 1ch     | <b>MANU</b>       | 8     | 80h           | Manual U value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1dh     | <b>MANV</b>       | 8     | 80h           | Manual V value                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 1eh     | <b>SH_Timing</b>  | 8     | 07h           | SH_Timing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     |

| 1fh     | <b>AVER_TAR_E</b> | 8     | 00h           | Black level target for E col.                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 |

| Address | Name                         | Width | Default value | Description                                                                                                                                                                   |

|---------|------------------------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 22h     | <b>AVER_TAR_O</b>            | 8     | 00h           | Black level target for E col.                                                                                                                                                 |

| 23h     | <b>GLGAINREG</b>             | 7     | 33h           | Green Gain                                                                                                                                                                    |

| 24h     | <b>AE_TAR1</b>               | 8     | 48h           | Y target.                                                                                                                                                                     |

| 25h     | <b>K_GLB_GAIN<br/>AE_LOC</b> | 8     | 64h           | Bit[7:4]:K_GLB_GAIN,LSB of GLB_GAIN slope.<br>Bit[3:0]:AE_LOC,INT_TIME and GLB_GAIN lock.                                                                                     |

| 26h     | <b>BLUE_GAIN_LOW_OUT</b>     | 6     | 0dh           | Bit[6:0]:The threshold of blue_gain_low_out                                                                                                                                   |

| 27h     | <b>BLUE_GAIN_HIGH_OUT</b>    | 6     | 10h           | Bit[6:0]:The threshold of blue_gain_high_out                                                                                                                                  |

| 28h     | <b>RED_GAIN_LOW_OUT</b>      | 6     | 09h           | Bit[6:0]:The threshold of red_gain_low_out                                                                                                                                    |

| 29h     | <b>RED_GAIN_HIGH_OUT</b>     | 6     | 24h           | Bit[6:0]:The threshold of red_gain_high_out                                                                                                                                   |

| 2ah     | <b>SC_CNTL3</b>              | 8     | 98h           | Bit[7]: 1'b1,pixel array reset interval also reset operate ;<br>1'b0,pixel array reset interval do nothing ;<br>Bit[6]: Reset interval address select.<br>Bit[5:0]: Reserved. |

| 2bh     | <b>VBLANK_PIX[7:0]</b>       | 8     | 00h           | Bit[7:0] :VBLANK_PIX[7:0].                                                                                                                                                    |

| 2ch     | <b>AVER_E</b>                | 8     | RO            | Read out black aver for EB/EG                                                                                                                                                 |

| 2dh     | <b>AVER_O</b>                | 8     | RO            | Read out black aver for OR/OG                                                                                                                                                 |

| 30h     | <b>SH_Timing</b>             | 7     | 4dh           | SH_Timing.                                                                                                                                                                    |

| 31h     | <b>SH_Timing</b>             | 8     | 03h           | SH_Timing.                                                                                                                                                                    |

| 32h     | <b>SC_CNTL1</b>              | 8     | 00h           | Bit[7]: 1'b1, VBLANK update netx frame.<br>1'b0, VBLANK update netx 2 frame.<br>Bit[6:0]: SH_Timing.                                                                          |

| 33h     | <b>SC_CNTL2</b>              | 8     | 26h           | Bit[7:5]: Reserved.<br>Bit[4]: 1'b1, GLB_GAIN_IN no delay.<br>1'b0, GLB_GAIN_IN delay one frame.<br>Bit[3:0]: Reserved.                                                       |

| 34h     | <b>R_COEF</b>                | 8     | 46h           | lens shading gain of R                                                                                                                                                        |

| 35h     | <b>G_COEF</b>                | 8     | 46h           | lens shading gain of G                                                                                                                                                        |

| 36h     | <b>B_COEF</b>                | 8     | 46h           | lens shading gain of B                                                                                                                                                        |

| 39h     | <b>PURE_TH</b>               | 8     | 58h           | Bit[7:4]: Pure b threshold, multiplied by 4.<br>Bit[3:0]: Pure r threshold, multiplied by 4.                                                                                  |

| 3ah     | <b>TSLB</b>                  | 8     | 00h           | Bit[7:2]:Reserved.<br>Bit[1:0]:serial mode<br>2'b00:DVP<br>2'b01:1 bit<br>2'b10:2 bits<br>2'b11:4 bits.                                                                       |

| 3bh     | <b>AWB_CB_LIM2</b>           | 8     | 18h           | Bit[7]: Reserved.<br>Bit[6:0]:AWB criterion: B, the threshold of B-G,for region 2.                                                                                            |

| 3ch     | <b>AWB_CR_LIM2</b>           | 8     | 18h           | Bit[7]: Reserved.                                                                                                                                                             |

| Address | Name               | Width | Default value | Description                                                                                                                                                                                                                                                              |

|---------|--------------------|-------|---------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|         |                    |       |               | Bit[6:0]:AWB criterion: R, the threshold of R-G,for region 2.                                                                                                                                                                                                            |

| 3dh     | <b>AWB_GR_LIM2</b> | 8     | 18h           | Bit[7]: Reserved.<br>Bit[6:0]:AWB criterion: B, the threshold of G-B,for region 2.                                                                                                                                                                                       |

| 3eh     | <b>AWB_BR_LIM2</b> | 8     | 18h           | Bit[7]: Reserved.<br>Bit[6:0]:AWB criterion: R, the threshold of G-R,for region 2.                                                                                                                                                                                       |

| 3fh     | <b>AWB_BR_LIM2</b> | 8     | 28h           | Bit[7]: Reserved.<br>Bit[6:0]:AWB criterion: BR, the threshold of  B+R-2*G ,for region 2.                                                                                                                                                                                |

| 40h     | <b>k0</b>          | 8     | 24h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 41h     | <b>k1</b>          | 8     | 30h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 42h     | <b>k2</b>          | 8     | 24h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 43h     | <b>k3</b>          | 8     | 1dh           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 44h     | <b>k4</b>          | 8     | 1ah           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 45h     | <b>k5</b>          | 8     | 14h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 46h     | <b>k6</b>          | 8     | 11h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 47h     | <b>k7</b>          | 8     | 0eh           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 48h     | <b>k8</b>          | 8     | 0dh           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 49h     | <b>k9</b>          | 8     | 0ch           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 4ah     | <b>SC_CNTL0D</b>   | 5     | 00h           | Bit[7:5]: Reserved.<br>Bit[4]: PDM_CNTL,<br>1'b0:POWERDOWN run free ;<br>1'b1: POWERDOWN Synchronous.<br>Bit[3]: Mirror,<br>1'b0: Normal image, 1'b1: Mirror image.<br>Bit[2]: Vertical Flip,<br>1'b0: Normal image, 1'b1: Vertically flip image.<br>Bit[1:0]: Reserved. |

| 4bh     | <b>k10</b>         | 8     | 0bh           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 4ch     | <b>k11</b>         | 8     | 09h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 4eh     | <b>k12</b>         | 8     | 09h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 4fh     | <b>k13</b>         | 8     | 08h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 50h     | <b>k14</b>         | 8     | 07h           | Gamma Correction Slop Coefficients                                                                                                                                                                                                                                       |

| 51h     | <b>TARGET1</b>     | 8     | 0dh           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[0] ).                                                                                                                                                                                       |

| 52h     | <b>TARGET2</b>     | 8     | 0eh           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[1] ).                                                                                                                                                                                       |

| 53h     | <b>TARGET3</b>     | 8     | 42h           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[2] ).                                                                                                                                                                                       |

| 54h     | <b>TARGET4</b>     | 8     | 4ch           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[3] ).                                                                                                                                                                                       |

| 55h     | <b>TARGET5</b>     | 8     | 76h           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[4] ).                                                                                                                                                                                       |

| 56h     | <b>TARGET6</b>     | 8     | 21h           | Bit[7:0]: Color Correction Coefficients low 8 bit (sign bits at TARGET_SIGN2[5] ).                                                                                                                                                                                       |

| Address | Name                                          | Width | Default value | Description                                                                                                                                                                                                          |

|---------|-----------------------------------------------|-------|---------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 57h     | <b>TARGET1_SK</b>                             | 8     | 37h           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[0],TARGET_H[0]}).                                                                                                 |

| 58h     | <b>TARGET2_SK</b>                             | 8     | 1eh           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[1],TARGET_H[1]}).                                                                                                 |

| 59h     | <b>TARGET3_SK</b>                             | 8     | afh           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[2],TARGET_H[2]}).                                                                                                 |

| 5ah     | <b>TARGET4_SK</b>                             | 8     | c5h           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[3],TARGET_H[3]}).                                                                                                 |

| 5bh     | <b>TARGET5_SK</b>                             | 8     | 55h           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[4],TARGET_H[4]}).                                                                                                 |

| 5ch     | <b>TARGET6_SK</b>                             | 8     | 18h           | Bit[7:0]: A light Color Correction Coefficients low 8 bit ({sign bits,hign 1 bit} at {TARGET_SIGN1[5],TARGET_H[5]}).                                                                                                 |

| 5dh     | <b>TARGET_H</b>                               | 6     | 00h           | Bit[5:0]: Control the highest value bit (bit[8]) of the A light coefficients.<br>Bit[5]:TARGET6_SK.<br>Bit[4]:TARGET5_SK.<br>Bit[3]:TARGET4_SK.<br>Bit[2]:TARGET3_SK.<br>Bit[1]:TARGET2_SK.<br>Bit[0]:TARGET1_SK.    |

| 5eh     | <b>GLB_GAIN_TH</b>                            | 8     | 20h           | Bit[7]: Glb_gain adjust switch.<br>1'b1: OFF,do not be affect by glb_gain.<br>1'b0: ON,do adjust for glb_gain.<br>Bit[5:0]: Used as glb_gain threshold for color martrix adjust, smaller value is for larger adjust. |

| 5fh     | <b>AWB_SPEED<br/>OUTDOOR_EN<br/>GNGAINREG</b> | 6     | 21h           | Bit[5:4]:AWB speed.<br>Bit[3]: Bit[7]: outdoor_en ,outdoor model control.<br>1'b0:off      1'b1:on<br>Bit[2:0]:G Channel Gain (Bit[2:0] is used as Green ain[5:3]).                                                  |

| 60h     | <b>AVER_E_I2C</b>                             | 8     | 10h           | Manual black level value for E col.                                                                                                                                                                                  |

| 61h     | <b>AVER_O_I2C</b>                             | 8     | 10h           | Manual black level value for O col.                                                                                                                                                                                  |

| 62h     | <b>SH_Timing</b>                              | 8     | 7dh           | SH_Timing.                                                                                                                                                                                                           |

| 63h     | <b>SH_Timing</b>                              | 7     | 0bh           | SH_Timing.                                                                                                                                                                                                           |

| 64h     | <b>SH_Timing</b>                              | 7     | 1ah           | SH_Timing.                                                                                                                                                                                                           |

| 65h     | <b>SH_Timing</b>                              | 7     | 34h           | SH_Timing.                                                                                                                                                                                                           |

| 66h     | <b>SH_Timing</b>                              | 7     | 40h           | SH_Timing.                                                                                                                                                                                                           |

| 67h     | <b>SH_Timing</b>                              | 8     | 9ah           | SH_Timing.                                                                                                                                                                                                           |

| 68h     | <b>SH_Timing</b>                              | 8     | 6bh           | SH_Timing.                                                                                                                                                                                                           |

| 69h     | <b>SH_Timing</b>                              | 8     | 6fh           | SH_Timing.                                                                                                                                                                                                           |

| 6ah     | <b>SH_Timing</b>                              | 8     | 71h           | SH_Timing.                                                                                                                                                                                                           |

| 6bh     | <b>SH_Timing</b>                              | 8     | 6dh           | SH_Timing.                                                                                                                                                                                                           |

| 6ch     | <b>SH_Timing</b>                              | 8     | a6h           | SH_Timing.                                                                                                                                                                                                           |

| 6dh     | <b>SH_Timing</b>                              | 8     | a7h           | SH_Timing.                                                                                                                                                                                                           |

| Address | Name              | Width | Default value | Description                                                                                                                                                                                                                                                                                                                                                                                                                         |

|---------|-------------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 6eh     | <i>SH_Timing</i>  | 7     | 09h           | SH_Timing.                                                                                                                                                                                                                                                                                                                                                                                                                          |

| 6fh     | <i>BRIGHT_ALL</i> | 7     | 00h           | Bit[6]:The sign for brightness adjust:<br>1:positive 0:negative<br>Bit[5:0]:value of brightness.                                                                                                                                                                                                                                                                                                                                    |

| 70h     | <i>IntCtr</i>     | 8     | 0fh           | Bit[7]:STOP_Sram--sram on/off<br>1'b0:on 1'b1:off<br>Bit[6]:Raw_Switch--output rawdata select<br>Bit[4]:G_off_En -- grid correction on/off<br>1'b0:off 1'b1:on<br>Bit[3]:Edge_Switch--edge enhancement on/off<br>1'b0:off 1'b1:on<br>Bit[2]:Clu_Switch--cluster correction on/off<br>1'b0:off 1'b1:on<br>Bit[1]:Bp_Switch--bad pixel correction on/off<br>1'b0:off 1'b1:on<br>Bit[0]:Lpf_Switch--denoise on/off<br>1'b0:off 1'b1:on |

| 71h     | <i>BpcCtr</i>     | 8     | 47h           | Bit[7:4]:Bp_TH1--threshold for badpixel<br>Bit[3]: Den_Out_En--denoise outdoor on/off<br>1'b0:on 1'b1:off<br>Bit[2]: Denoise_sel--edge mean for denoise(on/off)<br>1'b0:select center pixel for denoise<br>1'b1:select edge mean for denoise<br>Bit[1:0]:The gain value for cluster correction                                                                                                                                      |

| 72h     | <i>DenCtr1</i>    | 8     | 27h           | Bit[7:4]:Base_VAR<br>Bit[3:0]:Base_gl_gain                                                                                                                                                                                                                                                                                                                                                                                          |

| 73h     | <i>DenCtr2</i>    | 8     | 68h           | Bit[7:4]:Threshold to judge<br>Bit[3:0]:Int_tim_t                                                                                                                                                                                                                                                                                                                                                                                   |

| 74h     | <i>DenCtr3</i>    | 8     | a2h           | Bit[7:4]:The flat region threshold value(*2)<br>Bit[3]: Cen_Mean_sel<br>Bit[1:0]:Edg_En_Max                                                                                                                                                                                                                                                                                                                                         |

| 75h     | <i>DenCtr4</i>    | 8     | 89h           | Bit[7:4]:Y_Th--Y_AVER threshold Bit[3:2]:Int_tim_cho<br>Bit[0]: De_Low_En                                                                                                                                                                                                                                                                                                                                                           |

| 76h     | <i>DenCtr5</i>    | 8     | 8ah           | Bit[4]: Den_Y_Aver_En<br>Bit[3:0]: Den_Y_Aver_Th                                                                                                                                                                                                                                                                                                                                                                                    |

| 77h     | <i>EgeCtr1</i>    | 8     | 2fh           | Bit[7:4]: Edge_TH--threshold for edge detection(*2)<br>Bit[3:0]: Flat_TH--threshold for flat field(*2)                                                                                                                                                                                                                                                                                                                              |

| 78h     | <i>EgeCtr2</i>    | 8     | 23h           | Bit[7:4]:Edge_Gain_P<br>Bit[3:0]:Edge_Gain_N                                                                                                                                                                                                                                                                                                                                                                                        |

| 79h     | <i>EgeCtr3</i>    | 8     | 80h           | Bit[7:5]: Skin denoise strength.<br>Bit[4]: Gray_judge<br>Bit[3]: Edg_Off_Step<br>Bit[2]: Edg_Off_Mode<br>Bit[1:0]:Sobel_Min                                                                                                                                                                                                                                                                                                        |

| Address | Name                 | Width | Default value | Description                                                                                                                                                                                           |

|---------|----------------------|-------|---------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 7ah     | <b>EgeCtr4</b>       | 8     | 82h           | Bit[7]: Sobel_en--thin edge function on/off<br>1'b0:off 1'b1:on<br>Bit[4]: Low_Sh_Sw<br>Bit[3:0]:Edg_Off_base                                                                                         |

| 7bh     | <b>SobMax</b>        | 8     | ddh           | {Bit[7],Bit[3]}:Gain_Denoise<br>Bit[6:4]:Threshold for sobel difference( $2^{\text{Bit}[6:4]}$ )<br>Bit[2:0]:Threshold for sobel difference( $2^{\text{Bit}[2:0]}$ )                                  |

| 7ch     | <b>COM_SEL1</b>      | 8     | 97h           | Bit[7:4]:Y_DE_TH<br>Bit[3:0]:G_OFF_TH                                                                                                                                                                 |

| 7dh     | <b>TARGET_SIGN1</b>  | 6     | 36h           | Bit[5:0]: A light Color Correction Coefficients.<br>Bit[5]: TARGET_SEL6.<br>Bit[4]: TARGET_SEL5.<br>Bit[3]: TARGET_SEL4.<br>Bit[2]: TARGET_SEL3.<br>Bit[1]: TARGET_SEL2.<br>Bit[0]: TARGET_SEL1.      |

| 7eh     | <b>TARGET_SIGN2</b>  | 6     | 16h           | Bit[5:0]: Normal light Color Correction Coefficients.<br>Bit[5]: TARGET_SEL6.<br>Bit[4]: TARGET_SEL5.<br>Bit[3]: TARGET_SEL4.<br>Bit[2]: TARGET_SEL3.<br>Bit[1]: TARGET_SEL2.<br>Bit[0]: TARGET_SEL1. |

| 80h     | <b>AE_SPEED</b>      | 8     | 00h           | Bit[7:4] : The speed of adjusting from light to dark<br>Bit[3:0] : The speed of adjusting from dark to light                                                                                          |

| 81h     | <b>GLB_MIN1D</b>     | 8     | 1bh           | GLB_MIN1 8 Bits                                                                                                                                                                                       |

| 82h     | <b>GLB_MAX1D</b>     | 8     | 37h           | GLB_MAX1 8 Bits                                                                                                                                                                                       |

| 83h     | <b>GLB_MIN2D</b>     | 8     | 39h           | GLB_MIN2 8 Bits(test)                                                                                                                                                                                 |

| 84h     | <b>GLB_MAX2D</b>     | 8     | 5dh           | GLB_MAX2 8 Bits                                                                                                                                                                                       |

| 85h     | <b>GLB_MIN3D</b>     | 8     | 39h           | GLB_MIN3 8 Bits                                                                                                                                                                                       |

| 86h     | <b>GLB_MAX3D</b>     | 8     | 30h           | GLB_MAX3 8 Bits                                                                                                                                                                                       |

| 87h     | <b>GLB_GAIN0</b>     | 7     | 10h           | GLB_GAIN0 register.                                                                                                                                                                                   |

| 88h     | <b>Y_AVER</b>        | 8     | RO            | The Y_aver of the current frame                                                                                                                                                                       |

| 89h     | <b>INT_MID_I2C</b>   | 8     | 45h           | Bit[7:4]: The lock threshold<br>Bit[3:0]: INT_MID                                                                                                                                                     |

| 8ah     | <b>INT_STEP_50</b>   | 8     | 66h           | The low 8 Bits of the minimum integral time for every step to avoid flicker for 50HZ/60HZ light.                                                                                                      |

| 8bh     | <b>INT_STEP</b>      | 8     | 03h           | Steps of INT_TIM                                                                                                                                                                                      |

| 8ch     | <b>INT_TIM[12:8]</b> | 5     | RO            | Real integration time MSB.                                                                                                                                                                            |

| 8dh     | <b>INT_TIM[7:0]</b>  | 8     | RO            | Real integration time LSB.                                                                                                                                                                            |

| 8fh     | <b>INT_MIN</b>       | 8     | 82h           | INT_MIN select.                                                                                                                                                                                       |

| 90h     | <b>GAIN_BEG_4D</b>   | 8     | d7h           | Curve line :the fifth beginning point                                                                                                                                                                 |

| 91h     | <b>GAIN_END_4D</b>   | 8     | 30h           | Curve line :the fifth ending point                                                                                                                                                                    |

| Address | Name                            | Width | Default value | Description                                                                                                                                                                                                                                                                                    |

|---------|---------------------------------|-------|---------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 92h     | <b>GLB_HIGH</b>                 | 7     | 88h           | Bit[6:4]:The threshold of gain.<br>Bit[3]: The ending point of line 4,the msb.<br>Bit[2]: The starting point of line 4,the msb.<br>Bit[1]: The ending point of line 3,the msb.<br>Bit[0]: The starting point of line 3,the msb.                                                                |

| 94h     | <b>TAR_BASE0</b>                | 8     | 62h           | Bit[7:4]:(192+Bit[7 :4]*4 ) as threshold to judge one pixel whether to be over exposure pixel.<br>Bit[3:0]:Control the start of AE.                                                                                                                                                            |

| 95h     | <b>TAR_BASE1</b>                | 8     | 88h           | Bit[7:4]: is used to modify the difference of Y_AVER and modified AE_TAR) .the smaller TAR_BASE1[7:4] is ,the slower the AE adjusting.<br>Bit[3:0]:The smallest value the target brightness can achieve.(AE_TAR*TAR_BASE1[3:0]/16).the smaller TAR_BASE1[3:0] is,the quicker the AE adjusting. |

| 99h     | <b>DIG_GAIN_I2C</b>             | 8     | 10h           | The value of DIG_GAIN.                                                                                                                                                                                                                                                                         |

| 9ah     | <b>INT_TIM_TH</b>               | 8     | 18h           | Threshold for INT_TIME to judge outdoor scene.                                                                                                                                                                                                                                                 |

| 9dh     | <b>Gain_OR_Last</b>             | 8     | RO            | The value of gain_or_last[8:1] to get the GLB_GAIN0 through some operation                                                                                                                                                                                                                     |

| 9eh     | <b>YBRIGHT_TH</b>               | 8     | b6h           | Bit[7:4] : AE adjusting.<br>Bit[3:0]: Limit the speed of AE                                                                                                                                                                                                                                    |

| 9fh     | <b>AE_MODE<br/>DIG_GAIN_MAX</b> | 8     | 14h           | Bit[7]: Reserved.<br>Bit[6]: Control the adjustive speed of digital gain<br>1'b0 :Y_DIFF_D[6:1] (1 time)<br>1'b1 :Y_DIFF_D (2 times)<br>Bit[5]: Setps enable.<br>Bit[4]: AE is adjusted by men,<br>Bit[3:0]: DIG_GAIN_MAX                                                                      |

| a0h     | <b>AWB_CTR_SET</b>              | 8     | 09h           | Bit[7]: UPDATE_MODE<br>Bit[6]: J_CTRL6,sign white pixel selection<br>Bit[5]: J_CTRL5,<br>Bit[4]: J_CTRL4,combination1 selection.<br>Bit[3]: J_CTRL3<br>Bit[2]: J_CTRL2,PIXEL_WP_EN setting.<br>Bit[1]: J_CTRL1,combination2 selection.<br>Bit[0]: AWB_ENABLE:<br>1'b1:AWB on     1'b0:AWB off  |

| a1h     | <b>AWB_TH1_SET</b>              | 8     | 10h           | Bit[7:4]:AWB_LOCK, Auto white balance lock boundary.<br>Bit[3:2]:SKIN_BGAIN_TH_L.<br>Bit[1:0]:SKIN_RGAIN_TH_L.                                                                                                                                                                                 |

| a2h     | <b>BLU_GAIN_TH1</b>             | 6     | 0bh           | Bit[7:6]: Reserved.<br>Bit[5:0]: Minimum blue gain.                                                                                                                                                                                                                                            |